| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | |

| 7 | 8 | 9 | 10 | 11 | 12 | 13 |

| 14 | 15 | 16 | 17 | 18 | 19 | 20 |

| 21 | 22 | 23 | 24 | 25 | 26 | 27 |

| 28 | 29 | 30 | 31 |

- #@Transacional

- API

- propagation

- CQS

- SPOF

- hoisting

- CORS

- Java

- pessimistic lock

- NestJS 요청흐름

- RequestMappingHandlerMapping

- generic type

- HandlerMethod

- Generic method

- assertJ

- COPYOFRANGE

- cross-cutting concerns

- 벌크연산

- Transaction

- tracking-modes

- demand paging

- optimistic lock

- 프로그래머스

- wrapper class

- 역정규화

- type eraser

- ExceptionResolver

- IllegalStateException

- 단어변환

- TDZ

- Today

- Total

jingyulog

Virtual Memory 본문

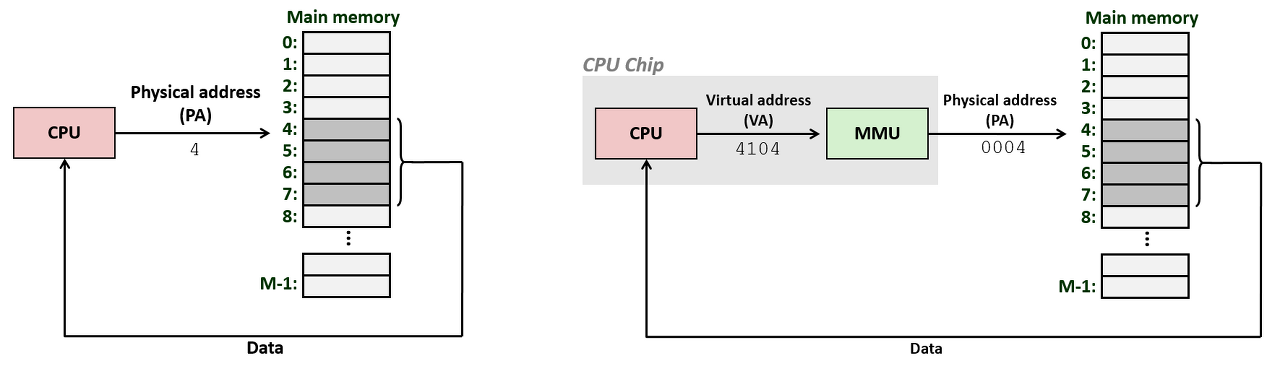

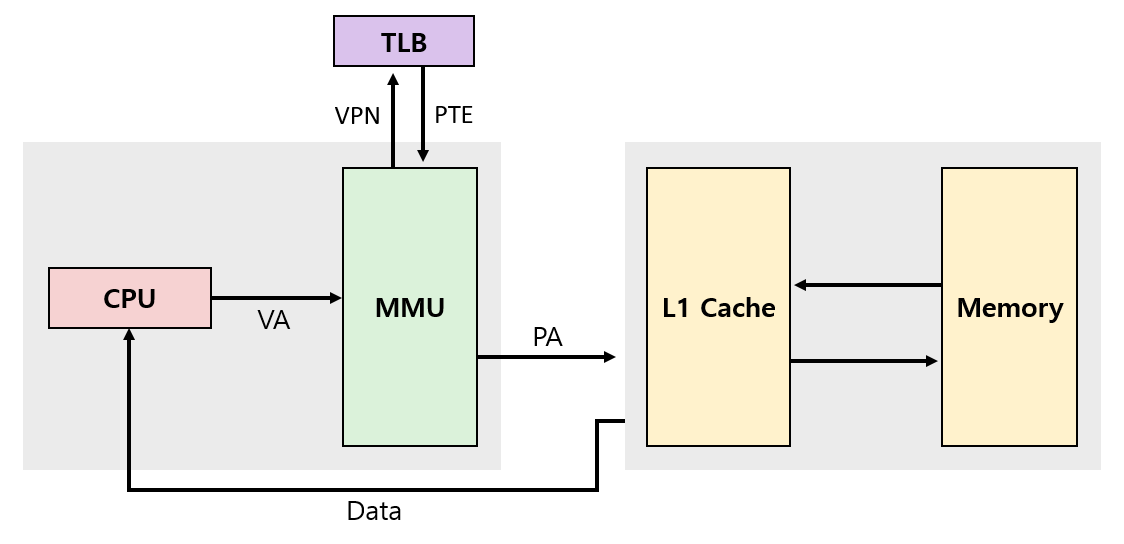

가상 메모리 시스템에서는 각 프로그램이 가상의 주소를 사용하도록 하며, CPU가 메모리 참조를 시도할 때는 MMU(Memory Management Unit)이라는 하드웨어 장치를 이용하여 해당 가상 주소(Virtual Address)를 실제 메인 메모리의 물리 주소로 변환하여 메모리 참조를 진행한다.

그렇다면 가상 메모리 기술은 왜 사용하는 것일까? 그 이유는 크게 3가지로 나눠서 생각해볼 수 있다. (Caching, Memory Management, Memory Protection).

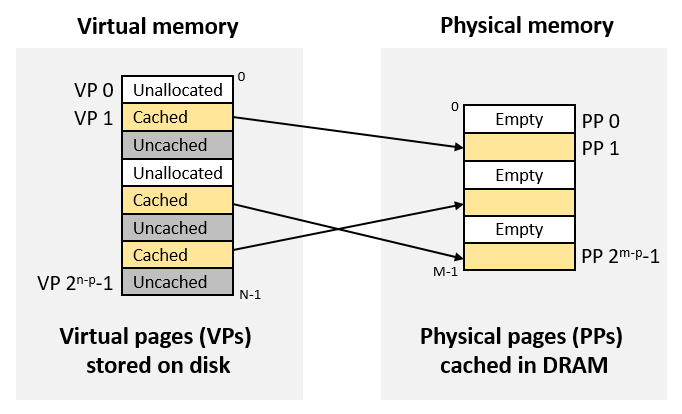

- 메인 메모리를 효율적으로 사용하기 위해서. 가상 메모리 시스템에서는 각 프로그램이 사용하는 가상 주소 공간을 우선 디스크에 저장해두고, 그 중에서 자주 사용되는 부분만 메인 메모리로 가져와서 사용한다. 즉, 메인 메모리를 디스크의 캐시로 사용하는 것이다. 이렇게 하나의 메인 메모리에 여러 프로그램의 데이터와 코드를 로드하는 것이 가능해진다.

- 메모리 관리를 단순화한다. 가상 메모리 시스템에서는 각 프로세스가 완전히 동일한 포맷의 가상 주소 공간을 가진다. 즉, 각 프로세스에게 혼자서 메인 메모리를 사용한다는 듯한 착각을 제공한다. 이는 링커 및 로더의 구현과 메모리 할당 방식 등을 단순화한다.

- 메모리 보호 매커니즘을 단순화한다. 왜냐하면, 가상 주소를 물리 주소로 변환할 때 참조하는 맵핑 테이블의 각 엔트리에는 해당 가상 주소에 대한 접근 권한이 명시되기 때문이다.

가상 메모리와 DRAM 캐시

가상 메모리는 디스크에 저장되는 연속적인 바이트들로 이루어진 배열을 의미하며, 해당 바이트 배열의 일부는 메인 메모리(DRAM 캐시)에 캐시된다. 그리고 캐시 메모리와 DRAM의 관계에서 Block이라는 단위를 사용하듯이, 메인 메모리와 디스크의 관계에서는 Page라는 단위를 사용한다. 즉, 디스크에 위치하는 Virtual Address Space의 각 페이지는 Virtual Page, 메인 메모리에 위치하는 Physical Address Space의 각 페이지는 Physical Page라고 부른다.

한편 DRAM 캐시는 캐시 메모리(메인 메모리의 캐시)에 비해 Miss Penalty가 매우 크다는 단점이 있다. 왜냐하면, DRAM과 SRAM의 속도 차이가 10배 정도인 반면에, 디스크와 DRAM의 속도 차이는 거의 10000배에 이르기 때문이다. 이로 인해 캐시 메모리와 DRAM 캐시는 2가지 측면에서 차이점을 가진다.

- Miss Penalty 처리 방식. DRAM 캐시의 경우, 디스크와 DRAM의 속도 차이가 상당히 크기 때문에 하드웨어 수준에서만 처리하기에는 낭비되는 시간이 너무 많다. 따라서 소프트웨어적인 처리를 가미한다. 예를들어, Miss Penalty 처리 도중에 문맥 전환.

- 캐시 메모리에 비해 DRAM 캐시는 Miss Penalty가 상당히 크기 때문에 Miss Rate를 최소화하기 위한 구조가 필요

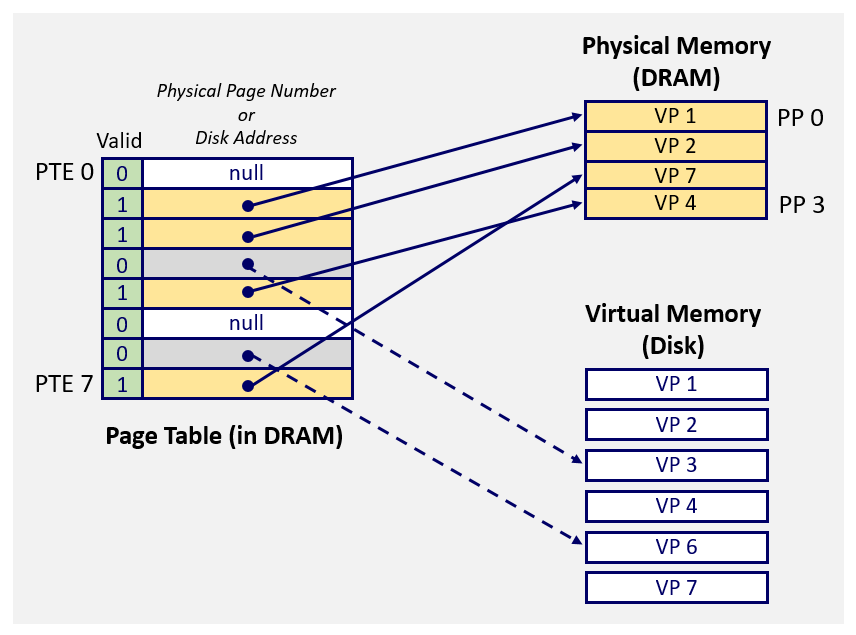

페이지 테이블(Page Table)

페이지 테이블은 가상 페이지와 물리 페이지 사이의 맵핑 정보를 담은 테이블로, 메인 메모리의 커널 영역에 저장되는 자료 구조 중 하나이다.

페이지 히트(Page Hit)

접근하고자 하는 가상 주소에 해당하는 Page Table Entry의 Valid 비트가 1이면, 해당 가상 페이지가 물리 페이지에 맵핑되어 있음을 의미한다. 이를 Page Hit 또는 DRAM 캐시 히트라고 한다. 이렇게 히트되면 해당 PTE 정보를 바탕으로 가장 주소를 물리 주소로 매핑하여 메인 메모리에 접근하기만 하면 된다.

페이지 미스(Page Miss) -> 페이지 폴트(Page Fault)

접근하려는 가상 주소에 해당하는 PTE의 Valid 비트가 0이고, 그곳에 디스크의 특정 위치 정보가 저장되어 있다면, 해당 가상 페이지가 물리 페이지에 매핑되어 있지 않음을 의미한다. 이를 페이지 미스 또는 DRAM 캐시 미스라고 부르고, 이러한 경우에는 Page Fault 예외가 발생하여 Page Fault Handler가 호출된다. 그러면 Page Fault Handler는 현재 메인 메모리에서 특정 물리 페이지를 선택하여 추방하고, 디스크에게 요청된 가상 페이지를 가져오도록 명령한 뒤에 문맥 전환을 통해 잠시 다른 프로세스에게 제어를 넘겨준다. 이후 과정은 다음과 같다.

- 디스크가 가상 페이지를 메인 메모리에 로드하는 작업을 완료하면, 인터럽트를 발생시켜서 문맥 전환을 통해 다시 페이지 폴트 핸들러의 프로세스로 제어를 옮긴다.

- 페이지 폴트 핸들러는 추방된 물리 페이지와 새로 들어온 물리 페이지의 정보를 바탕으로 PTE를 갱신하고, 페이지 폴트를 일으켰던 명령어의 위치로 다시 리턴하여 해당 명령어를 재실행한다.

- 이번에는 페이지 히트가 발생하므로 위에서 설명한 방식대로 메모리 참조를 진행하면 된다.

페이지 할당 (Allocating Pages)

유저 프로세스로 실행되는 프로그램이 추가적으로 힙 영역을 할당하려고 시도하면(malloc), 커널은 적절한 크기의 연속적인 가상 페이지들을 디스크에 할당하고, 그것들에 해당하는 PET들을 페이지 테이블에 새로 만들어준다. 그렇게 생성된 각각의 PET는 Valid 비트가 0이며, 해당 가상 페이지가 디스크의 어느 위치에 할당되어 있는지에 대한 정보를 담게 된다.

작업 집합 (Working Set)

작업 집합은 프로그램이 자주 사용하는 가상 주소 공간을 의미한다. 만약 프로그램이 시간적 지역성을 잘 활용할 수 있도록 짜여있으면, 작업 집합의 크기는 작을 것이다. 따라서 만약에 작업 집합의 크기가 메인 메모리의 크기보다 작으면, 최초의 미스 이후에는 메모리 참조에 있어서 굉장히 좋은 성능을 보일 것이다. 반면에 작업 집합의 총 크기가 메인 메모리의 크기보다 크다면, 특정 가상 페이지가 물리 페이지에 매핑이 되어있다가 해당 물리 페이지가 다시 추방당하는 과정이 계속 반복될 것이다. 이러한 현상을 Thrashing이라고 한다.

주소 변환 (Address Translation)

- 먼저 변환하고자 하는 가상 주소에 해당하는 PTE를 찾아간다. 만약 PTE의 Valid 비트가 0인데 그곳에 디스크의 특정 위치 정보가 저장되어 있다면, 해당 가상 페이지가 물리 페이지에 맵핑되어 있지 않음을 의미하므로 페이지 폴트 예외가 발생한다.

- PTE의 Valid 비트가 1이면 해당 가상 페이지가 물리 페이지에 맵핑되어 있음을 의미하므로, 해당 PTE에서 맵핑된 물리 페이지의 번호(PPN)를 알아낸다. 그리고 여기에 가상 주소의 페이지 오프셋 정보(VPO)를 덧붙여 주면 물리 주소가 완성된다.

- 참고로 페이지 테이블 자체의 시작 주소는 CPU 내 페이지 테이블 베이스 레지스터(Page Table Base Register, PTBR)라는 곳에 저장이 되어 있다.

TLB (Translation Lookaside Buffer)

TLB는 메인 메모리에 존재하는 페이지 테이블의 캐시로서 MMU 내부에 존재하는 작은 하드웨어 버퍼 장치를 의미한다. 즉, TLB에는 참조되는 빈도가 높은 페이지 테이블 엔트리가 저장된다.

메모리 참조 전체 과정

우선 프로그램에서 메모리를 접근하는 경우를 살펴보자.

- PC에 저장된 값을 바탕으로 명령어 메모리에서 명령어를 읽어오는 경우

- 데이터 메모리를 접근하는 특정 명령어(popq, pushq, movq)를 실행하는 경우

그리고 이러한 메모리 접근은 전부 가상 주소에 근거하여 이루어진다. 그럼 만약 CPU가 메모리 접근을 위해 특정 가상 주소를 발생시켰다고 상황을 가정해보자.

- 그러면 우선 PTE를 가져오기 위해 TLB를 방문한다.

- 만약 TLB 히트라면, 그곳에 존재하는 PTE를 바탕으로 가상 주소를 물리 주소로 변환한다. 참고로 TLB 히트는 해당 가상 페이지가 물리 페이지에 반드시 매핑되어 있음을 보장한다.

- 반면에 TLB 미스라면, 다시 2가지 경우로 나뉜다.

- 먼저 해당 가상 페이지가 물리 페이지에 매핑되어 있는 경우이다. 이러한 경우에는 메모리 계층에 접근하여 해당 가상 페이지에 대한 PTE를 가져오고, 이를 TLB에 반영해준다.

- 다음은 해당 가상 페이지가 물리 페이지에 매핑되어 있지 않은 경우이다. 이러한 경우에는 메모리 계층에 접근하여 가져오는 PTE의 정보를 보고, Page Fault 예외를 발생시킨다. 그러면 특정 페이지를 추방하고, 새로운 페이지를 가져온 뒤에 이에 맞게 PTE와 TLB의 정보를 갱신해준다. 이제 다시 Page Fault를 유발했던 명령어를 재실행하면, TLB 미스인데 해당 가상 페이지가 물리 페이지에 매핑되어 있는 경우가 된다.

인텔 코어 i7 CPU

인텔 코어 i7 CPU는 48비트의 가상 주소 공간(256TB)과 52비트의 물리 주소 공간(4PB)을 가지며, 호환성을 지키기 위해 32비트의 가상/물리 주소 공간(4GB)도 지원한다.

다음 그림은 인텔 코어 i7의 메모리 시스템을 요약한 그림이다.

그리고 다음 그림은 인텔 코어 i7 CPU의 전체적인 메모리 참조 과정을 요약한 것이다.

'책 - 요약 정리 > CSAPP' 카테고리의 다른 글

| Network Programming (0) | 2023.11.17 |

|---|---|

| Exceptional Control Flow (0) | 2023.11.07 |

| linking (0) | 2023.11.07 |

| CSAPP - Procedures (1) | 2023.11.01 |